Digital Logic

Binary Systems

Estimated Marks : 5

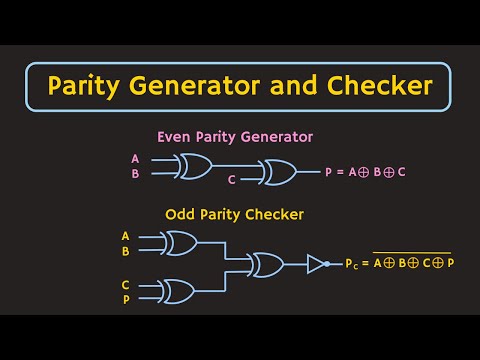

These topics build foundation for coming chapters. Become very familiar with base conversion and complements. Also, parity bits checking is highly important for exam.

Base Conversion - Part 1

Base Conversion - Part 1 Base Conversion - Part 2

Base Conversion - Part 2 Base Conversion - Part 3

Base Conversion - Part 3 Complement: 1s and 2s

Complement: 1s and 2s Complement: 9s & 10s

Complement: 9s & 10s Binary Codes - Introduction

Binary Codes - Introduction BCD and Excess 3

BCD and Excess 3 Subtraction: 9s & 10s

Subtraction: 9s & 10s Subtraction: 1s & 2s

Subtraction: 1s & 2s Parity Introduction

Parity Introduction Bwih7_AT1oI

Bwih7_AT1oI Integrated Circuit

Integrated Circuit- 1Base Conversion - Part 1

- 2Base Conversion - Part 2

- 3Base Conversion - Part 3

- 4Complement: 1s and 2s

- 5Complement: 9s & 10s

- 6Binary Codes - Introduction

- 7BCD and Excess 3

- 8Subtraction: 9s & 10s

- 9Subtraction: 1s & 2s

- 10Parity Introduction

- 11Bwih7_AT1oI

- 12Integrated Circuit

Boolean Algebra

Estimated Marks : 5

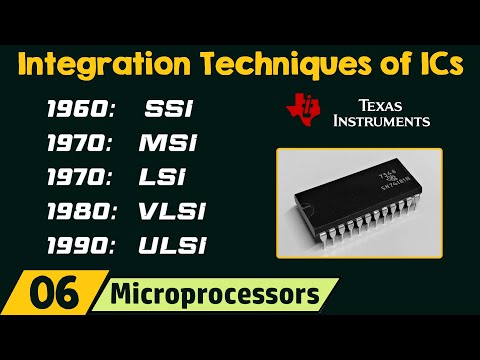

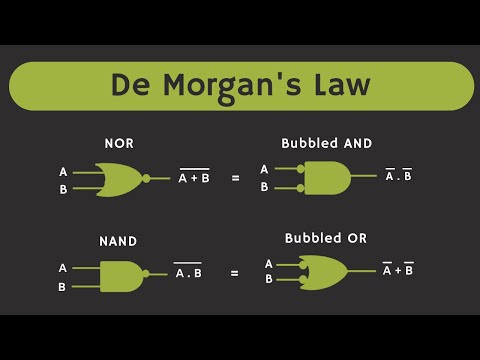

De Morgan's Law and NAND/NOR gate as universal gates are the most important topic from here. They are easy and repeatedly asked. IC terms are sometime asked in short notes type question.

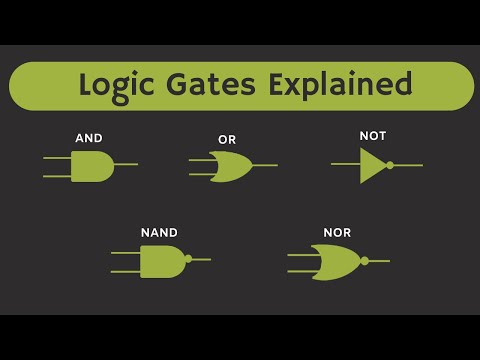

Logic Gates

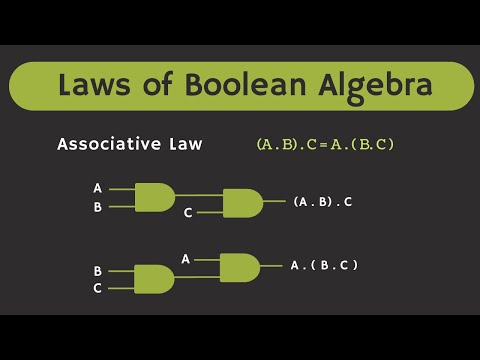

Logic Gates Boolean Algebra Laws

Boolean Algebra Laws Demorgans Law

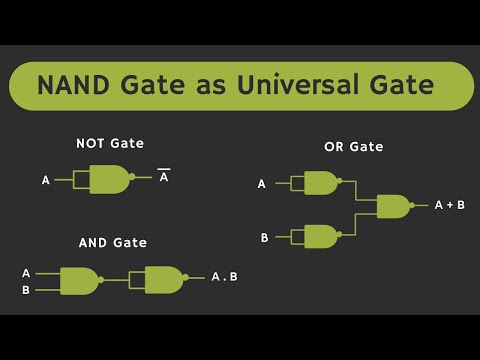

Demorgans Law Universal Gate - NAND

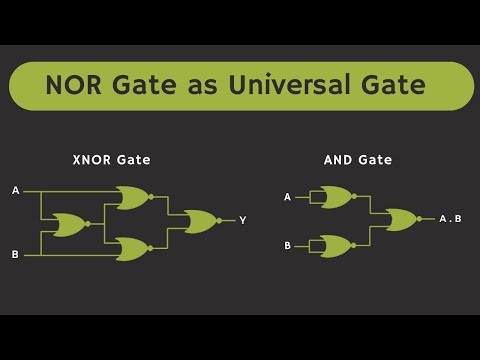

Universal Gate - NAND Universal Gate - NOR gate

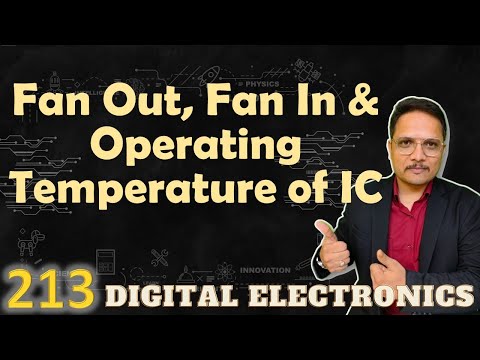

Universal Gate - NOR gate IC terms - 1

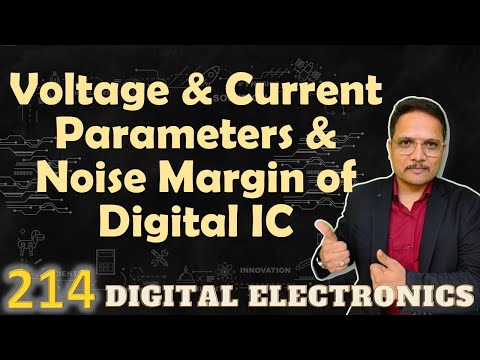

IC terms - 1 IC terms - 2

IC terms - 2 IC terms - 3

IC terms - 3- 1Logic Gates

- 2Boolean Algebra Laws

- 3Demorgans Law

- 4Universal Gate - NAND

- 5Universal Gate - NOR gate

- 6IC terms - 1

- 7IC terms - 2

- 8IC terms - 3

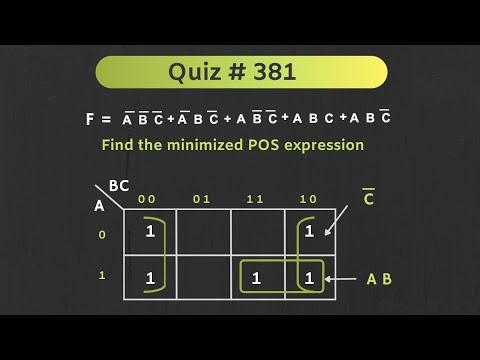

Simplification of Boolean Functions

Estimated Marks : 10

K-Map is very important. Spend as much time you can practising this. Watch all videos of this chapter very carefully. Most students make mistakes in Dont Care Conditions.

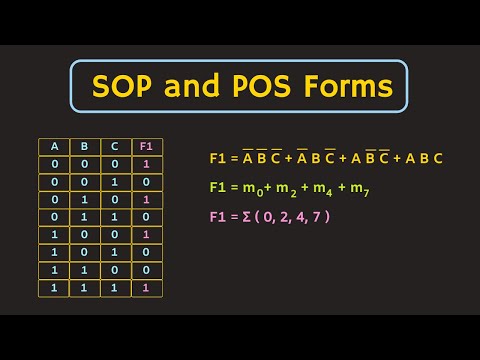

SOP and POS

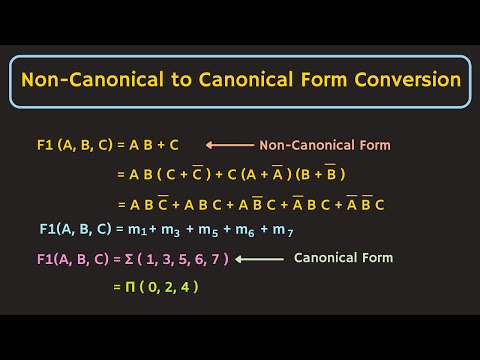

SOP and POS Form Conversion

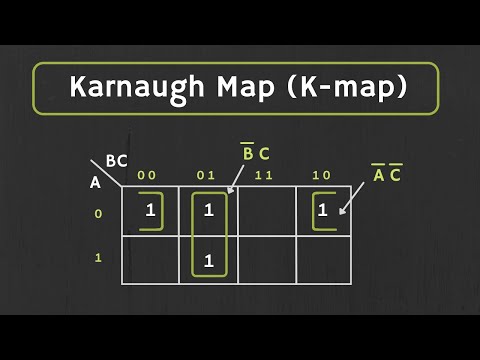

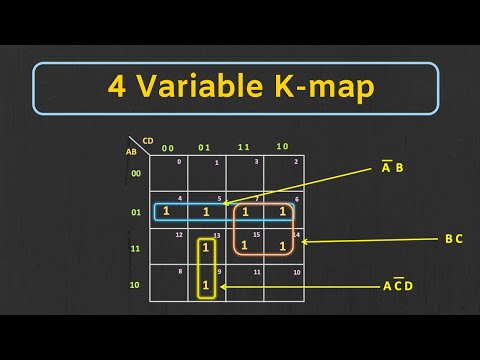

Form Conversion K - Map

K - Map K-Map - Example Question

K-Map - Example Question K-Map - Part 2

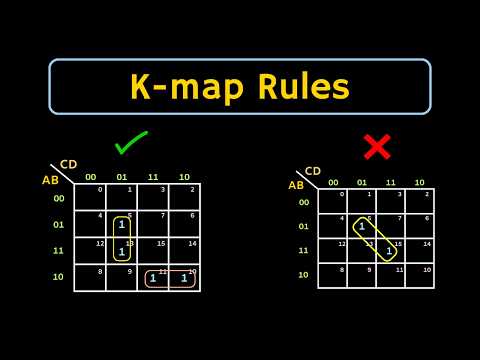

K-Map - Part 2 K-Map Rules

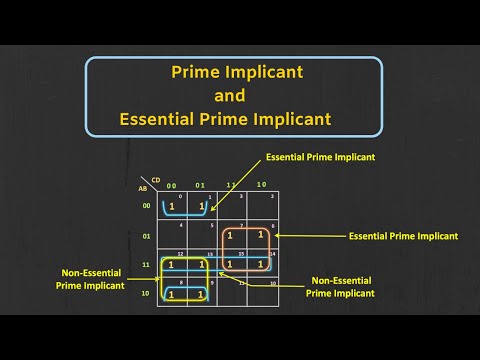

K-Map Rules Prime Implicant

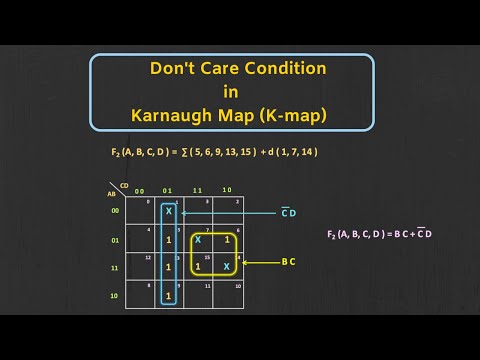

Prime Implicant Don't Care Condition

Don't Care Condition NAND Gate Implementation

NAND Gate Implementation - 1SOP and POS

- 2Form Conversion

- 3K - Map

- 4K-Map - Example Question

- 5K-Map - Part 2

- 6K-Map Rules

- 7Prime Implicant

- 8Don't Care Condition

- 9NAND Gate Implementation

Combinational Circuits

Estimated Marks : 15

Here you will be asked to make several circuit designs like Adder, Subtractor etc. They are asked in 5 marks questions. You will also find 10 marks question asking to implement function using Decoder or MUX.

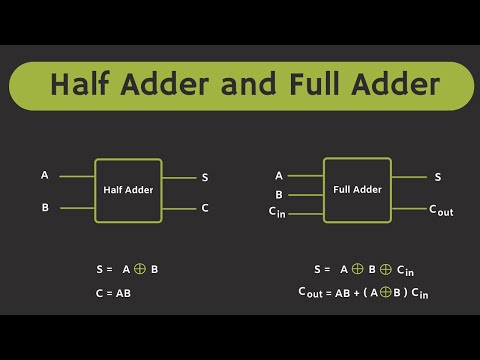

Adder

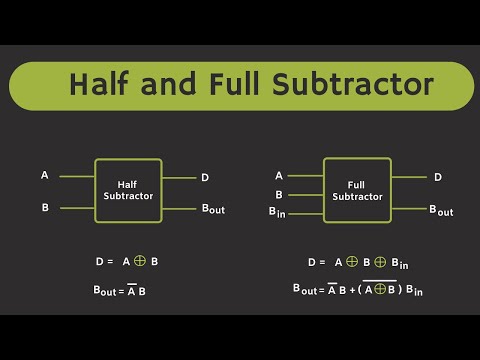

Adder Subtractor

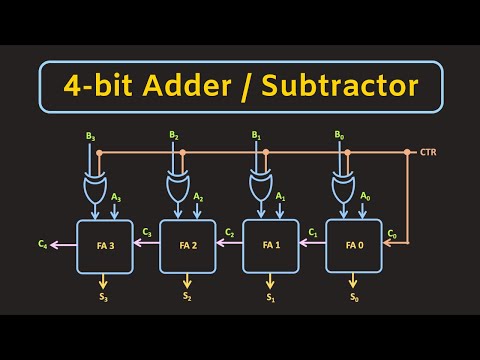

Subtractor 4 bit Adder/Subtractor

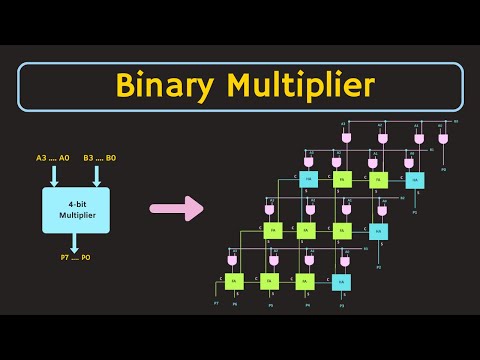

4 bit Adder/Subtractor Multiplier

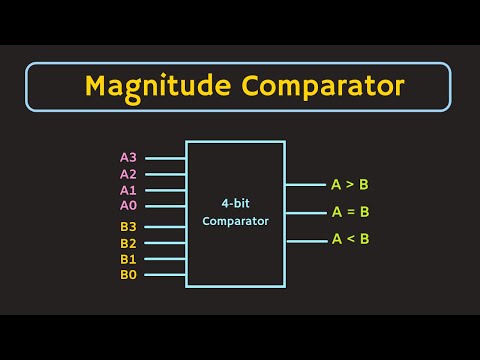

Multiplier Comparator

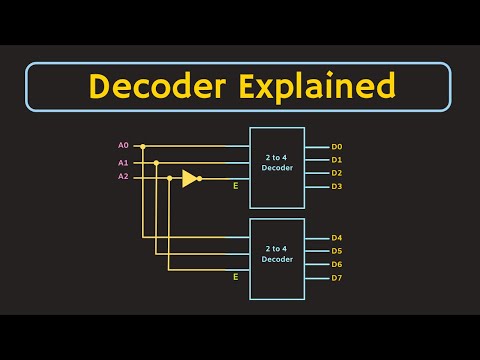

Comparator Decoder

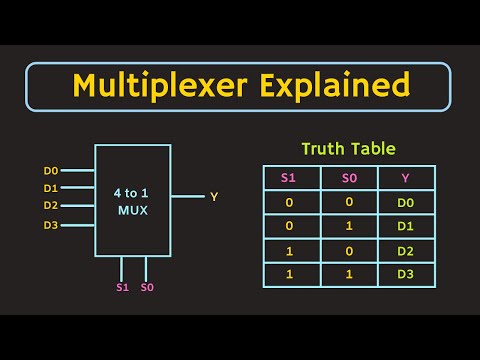

Decoder Multiplexer

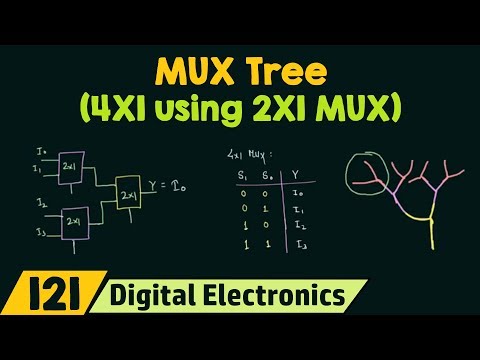

Multiplexer 4X1 MUX using 2X1 MUX

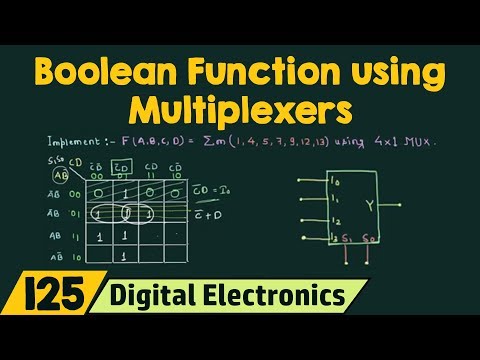

4X1 MUX using 2X1 MUX Implement Function with MUX

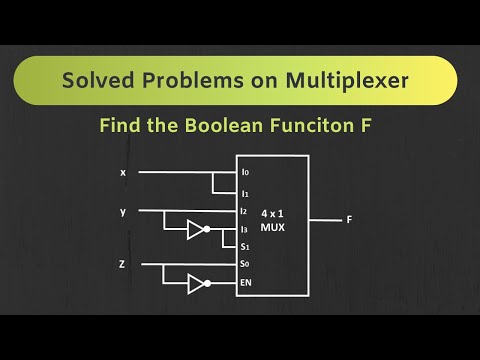

Implement Function with MUX Multiplexer - Questions

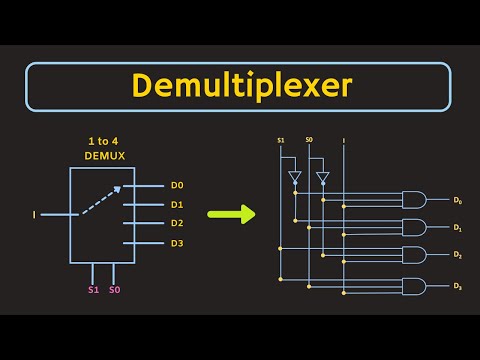

Multiplexer - Questions Demultiplexer

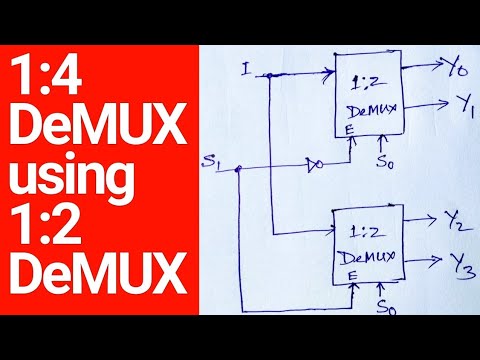

Demultiplexer 1x4 demux from 1x2

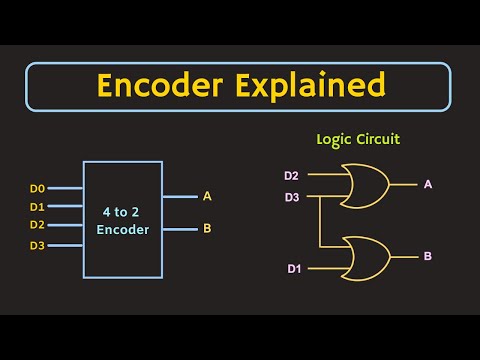

1x4 demux from 1x2 Encoder

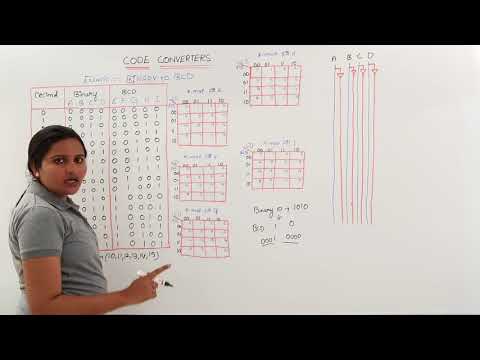

Encoder Binary to BCD

Binary to BCD Binary to Gray

Binary to Gray BCD to Excess 3

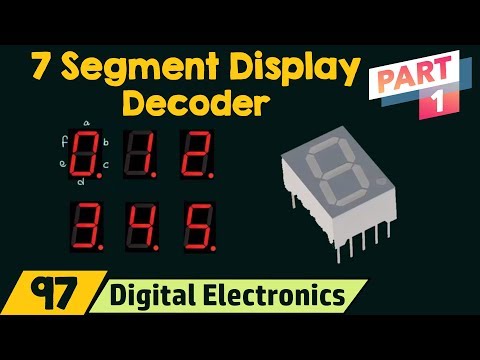

BCD to Excess 3 Seven Segment Display

Seven Segment Display- 1Adder

- 2Subtractor

- 34 bit Adder/Subtractor

- 4Multiplier

- 5Comparator

- 6Decoder

- 7Multiplexer

- 84X1 MUX using 2X1 MUX

- 9Implement Function with MUX

- 10Multiplexer - Questions

- 11Demultiplexer

- 121x4 demux from 1x2

- 13Encoder

- 14Binary to BCD

- 15Binary to Gray

- 16BCD to Excess 3

- 17Seven Segment Display

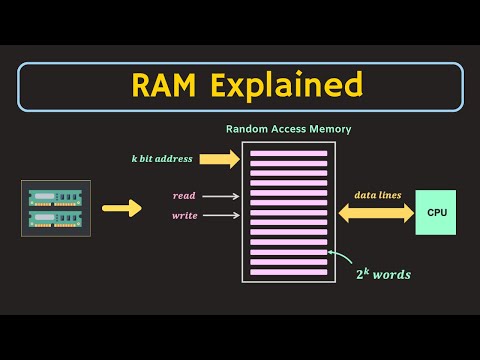

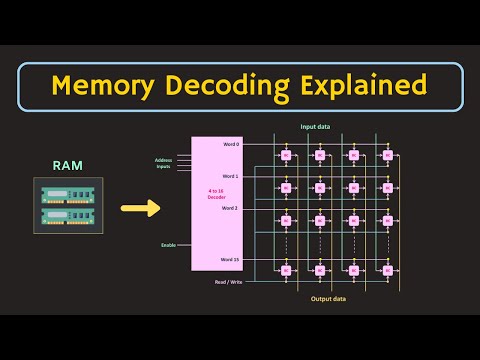

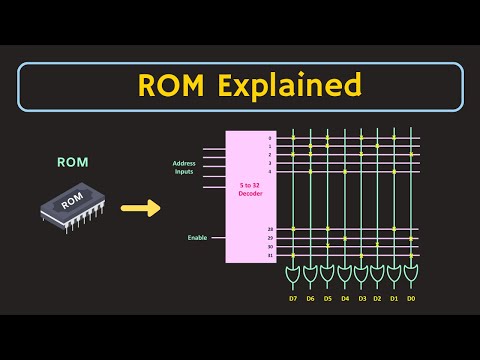

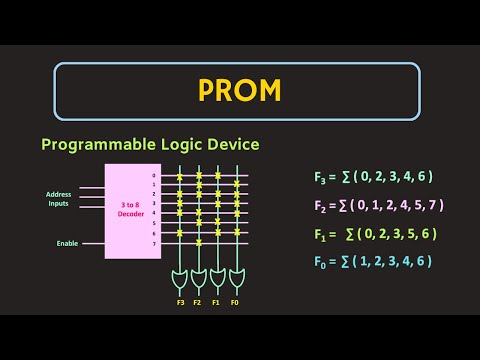

RAM, ROM, PLA and PAL

Estimated Marks : 5

There will a long Question from this alongside multiplexer and decoder

RAM - 1

RAM - 1 RAM - 2

RAM - 2 ROM - Introduction

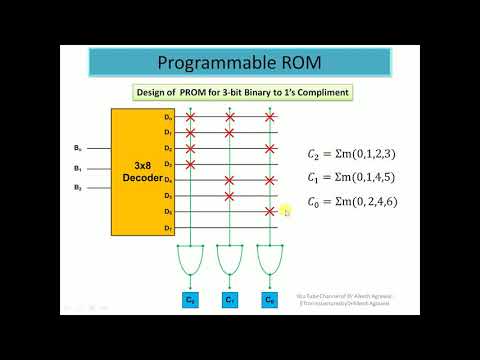

ROM - Introduction PROM

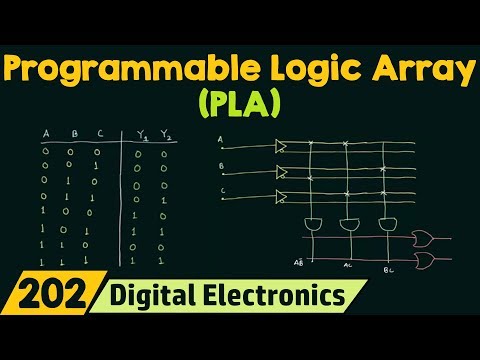

PROM PLA

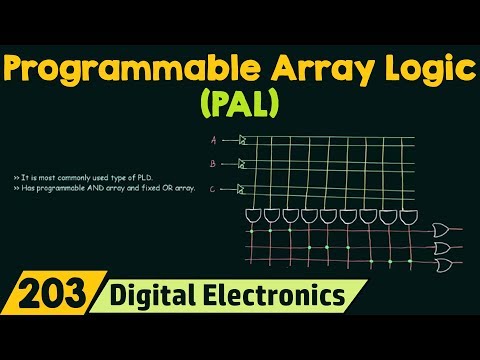

PLA PAL

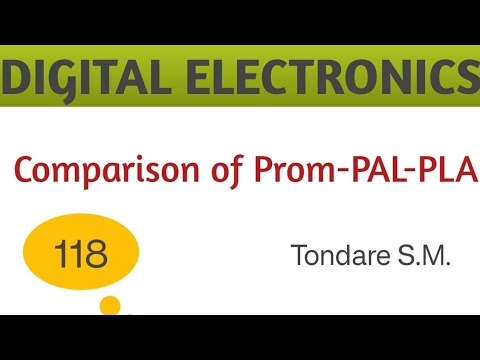

PAL ROM vs PLA vs PAL

ROM vs PLA vs PAL PLA, PAL, ROM - Summary

PLA, PAL, ROM - Summary- 1RAM - 1

- 2RAM - 2

- 3ROM - Introduction

- 4PROM

- 5PLA

- 6PAL

- 7ROM vs PLA vs PAL

- 8PLA, PAL, ROM - Summary

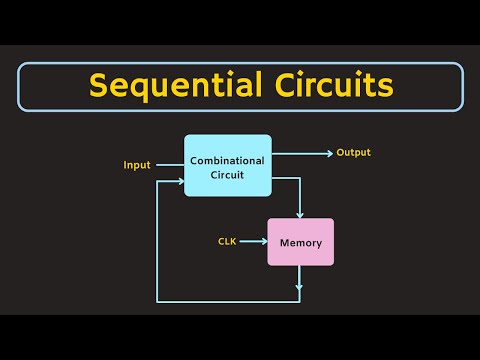

Sequential Logic

Estimated Marks : 5

This chapter is harder than previous and require a lot of attention at first. Heavy marks weightage comes from this chapter and Counters. \

Introduction

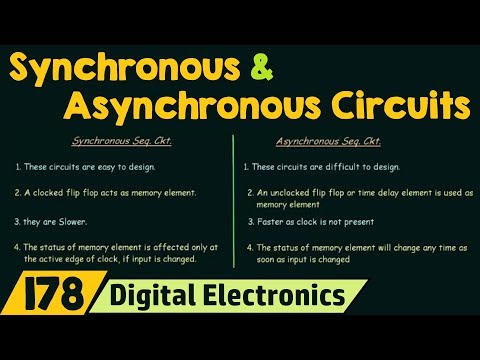

Introduction Sync vs Async Sequential

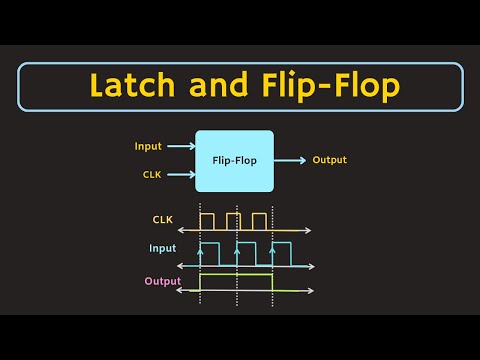

Sync vs Async Sequential Latch & FlipFlop

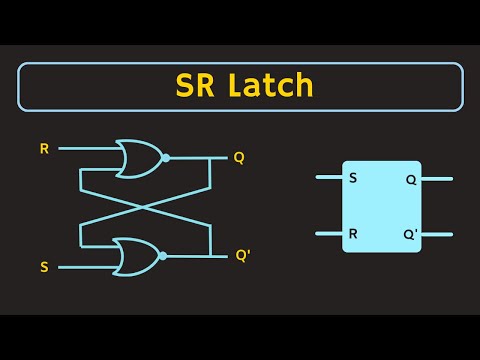

Latch & FlipFlop SR Latch

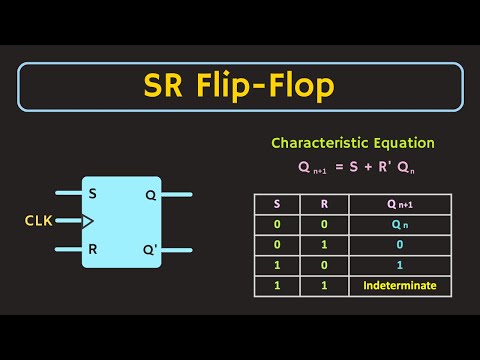

SR Latch SR FlipFlop

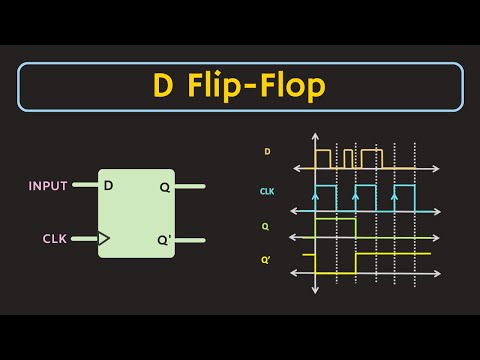

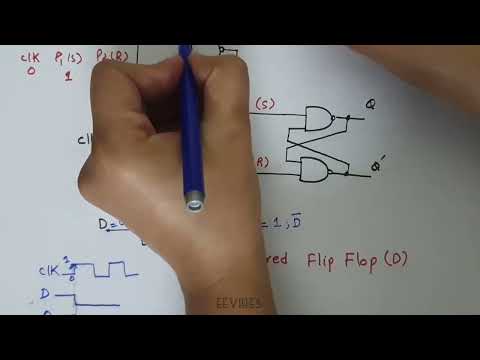

SR FlipFlop D FlipFlop

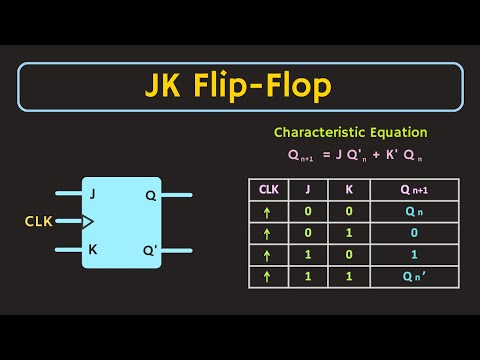

D FlipFlop JK FlipFlop

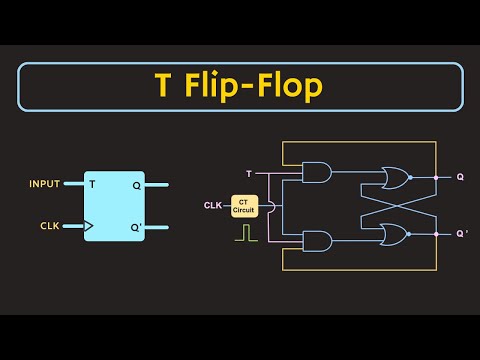

JK FlipFlop T FlipFlop

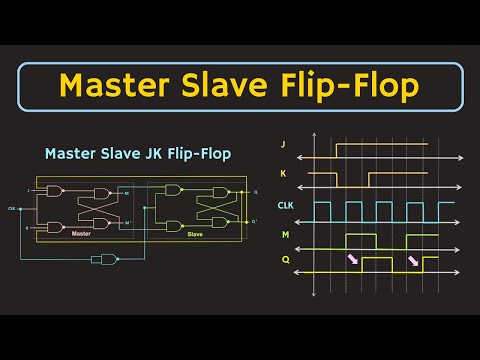

T FlipFlop Master Slave FlipFlop

Master Slave FlipFlop Edge-Triggered D Flip Flop

Edge-Triggered D Flip Flop- 1Introduction

- 2Sync vs Async Sequential

- 3Latch & FlipFlop

- 4SR Latch

- 5SR FlipFlop

- 6D FlipFlop

- 7JK FlipFlop

- 8T FlipFlop

- 9Master Slave FlipFlop

- 10Edge-Triggered D Flip Flop

Register and Counter

Estimated Marks : 25

Maybe the hardest topic. Only come to this chapter after you are comfortable with flip flops. State diagram, table and circuit is very important to understand so be very attentive. If you are just before exams, study up to Video number 12

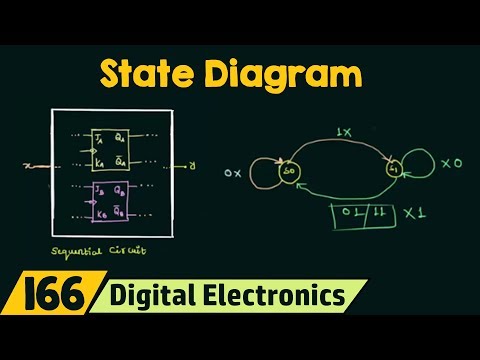

State Table, Diagram, Equation

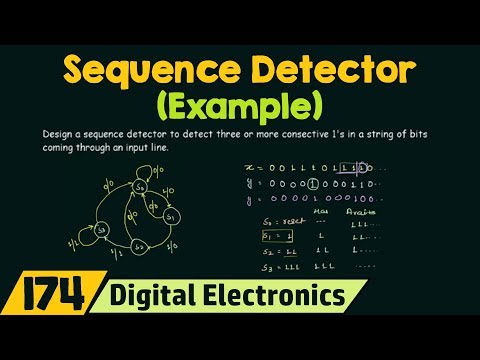

State Table, Diagram, Equation Sequence Detect

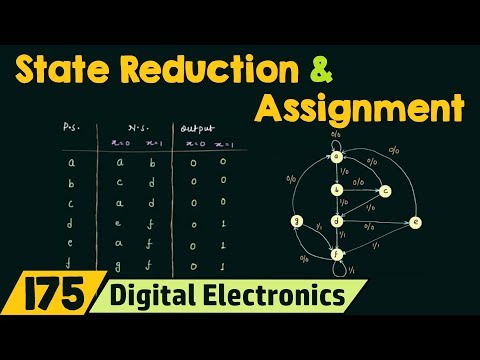

Sequence Detect State Reduction

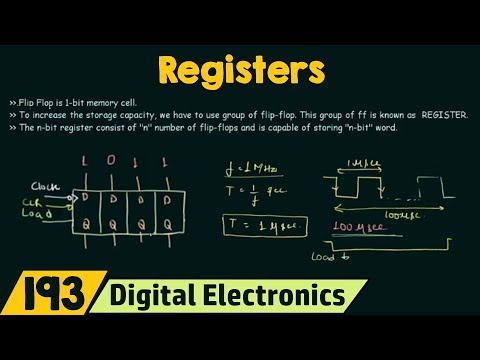

State Reduction Registers Intro

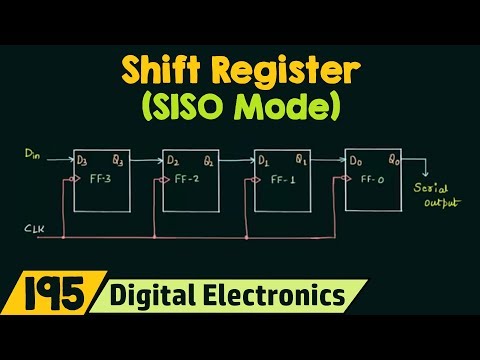

Registers Intro  SISO

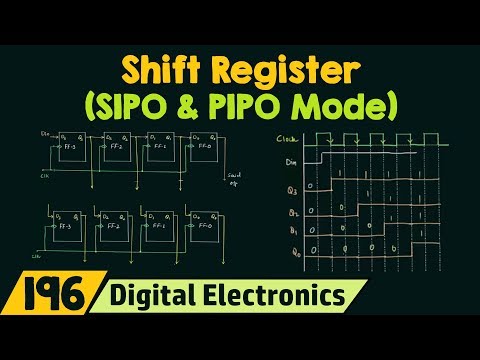

SISO SIPO & PIPO

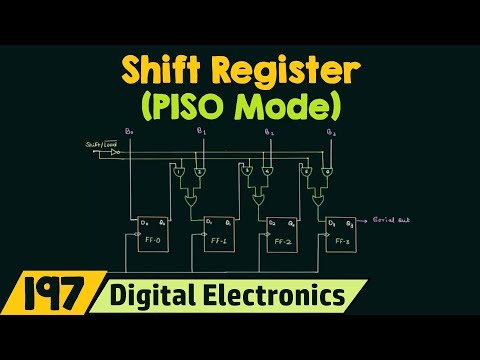

SIPO & PIPO PISO

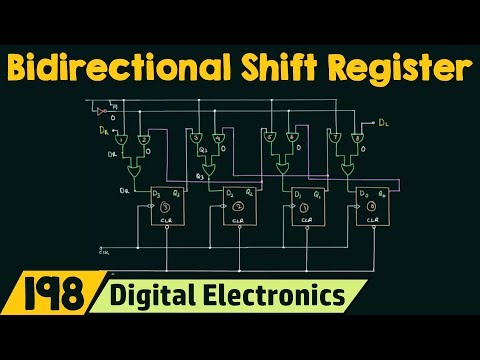

PISO Bidirectional Shift Register

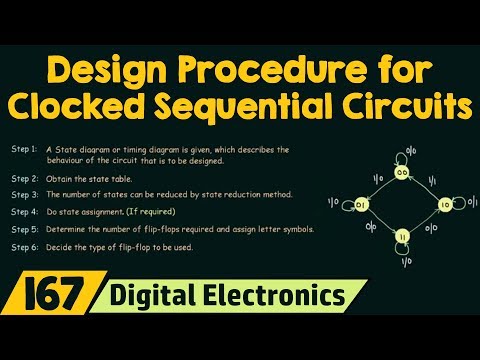

Bidirectional Shift Register Design Process

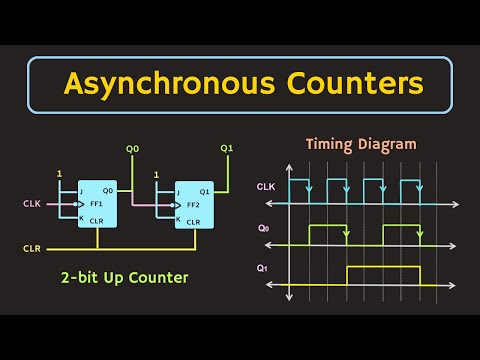

Design Process Asynchronous Counters (Ripple Counters)

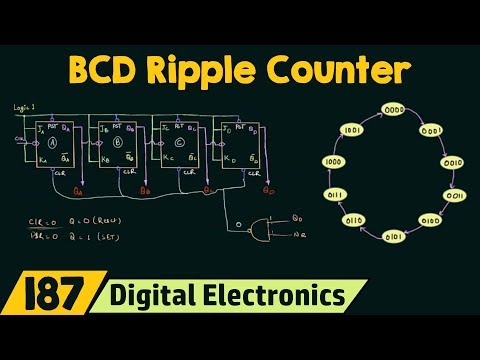

Asynchronous Counters (Ripple Counters) BCD Ripple Counter

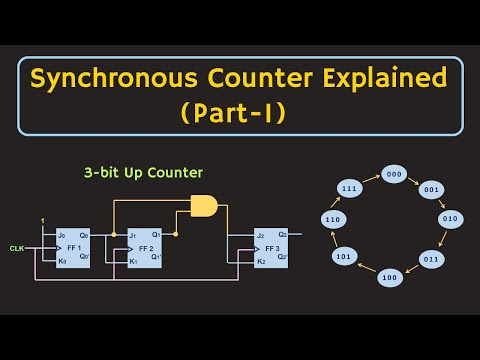

BCD Ripple Counter Synchronous Counters

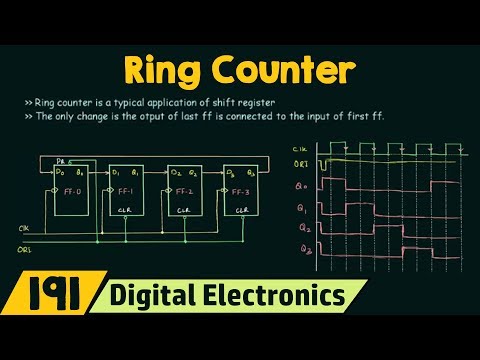

Synchronous Counters Ring Counter

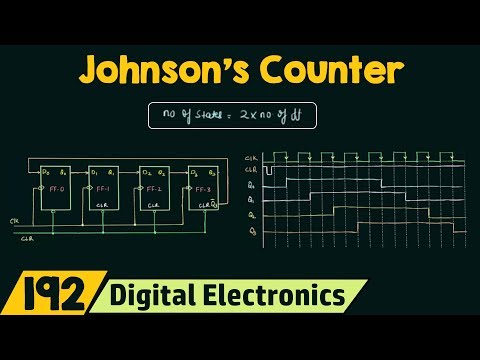

Ring Counter  Johnson's Counter

Johnson's Counter MOD 3 Counter

MOD 3 Counter Random Sequence

Random Sequence- 1State Table, Diagram, Equation

- 2Sequence Detect

- 3State Reduction

- 4Registers Intro

- 5SISO

- 6SIPO & PIPO

- 7PISO

- 8Bidirectional Shift Register

- 9Design Process

- 10Asynchronous Counters (Ripple Counters)

- 11BCD Ripple Counter

- 12Synchronous Counters

- 13Ring Counter

- 14Johnson's Counter

- 15MOD 3 Counter

- 16Random Sequence